Best chiplet CPUfor edge to cloud

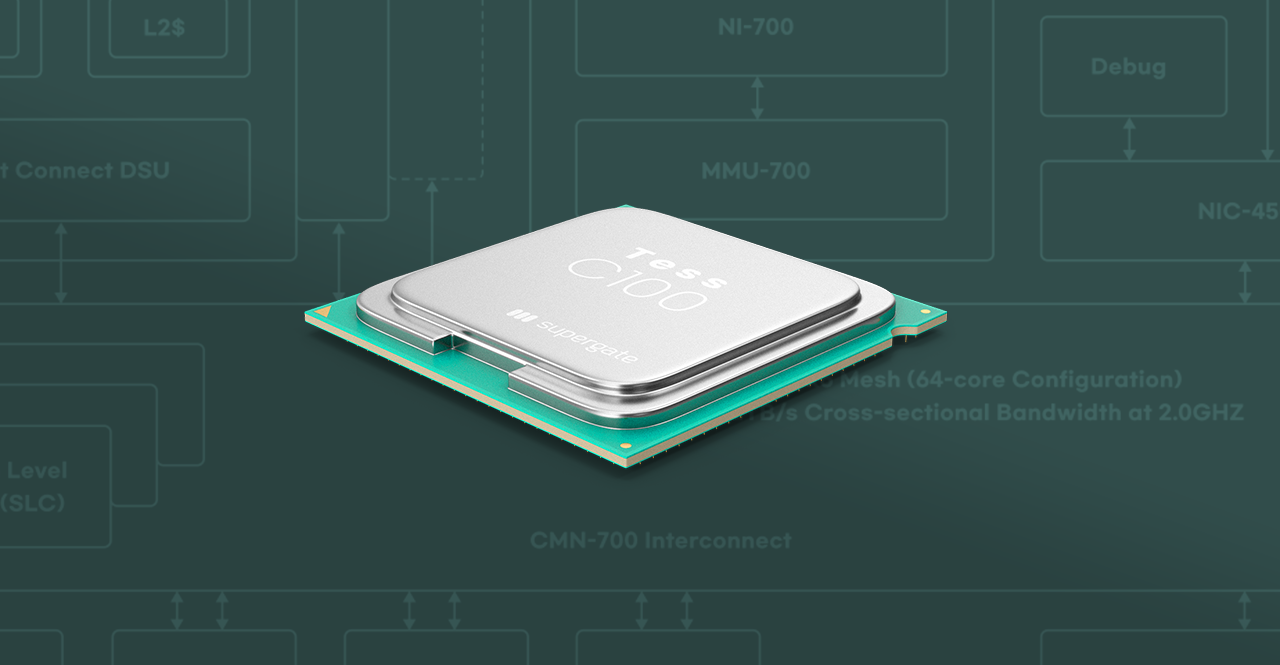

Tess C100

Overview

Next-Generation Chiplet ArchitectureNeoverse N2

The Tess C100 is a next-generation chiplet architecture designed to integrate and manage various functions such as CPU, GPU, and NPU. Based on the Arm Neoverse N2 architecture, the Tess C100 provides outstanding performance across all domains, from data centers to edge computing.

Key Features

Scalability

The architecture allows for easy scalability, making it suitable for a wide range of applications and workloads.

Energy Efficiency

The Tess C100 is designed with energy efficiency in mind, helping to reduce operational costs while maintaining high performance.

Specifications

CPU

- ARM Neoverse N2 core (Armv9.0-A Architecture)

- SVE (Scalable Vector Extension) version 2

- 32 core / chip

64 core / socket (UCIe - CML_SMP)

128 (max) core with 2 socket (PCIe - CML_SMP) - Clock Speed : 3.0 GHz

Cache

- L1 : 64KB

- L2 : 1MB

- System Level : 64MB

Memory

- DDR5-4800 RDIMM

- 4x RDIMM / chip

Interconnects

4x UCIe 1.1

- Die-to-Die Link : Standard Package

- 2x UCIe 1.1 x64 : CML_SMP

- 2x UCIe 1.1 x64 : Non-Coherent I/O (AXI)

4x PCIe Gen5 x16

- CXL 2.0 (Type 3)

- CML_SMP

Manufacturing Process

TSMC 5nm

Technical

Partnership

Arm Approved Design Partner (AADP)

Supergate is a design partner approved by Arm. It was designed as Cortex-A53 for its autonomous head design and used Arm Nevers V1 for the saga of supercomputing.

Arm Total Design (ATD)

Asicland is the only TSMC VCA in Korea and the ATD partner of Arm. It is developing the Compute Sub-system (CSS) platform of Neoverse N2 with TSMC 5nm.